题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

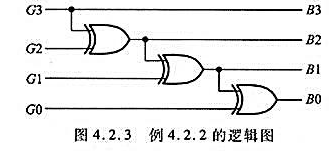

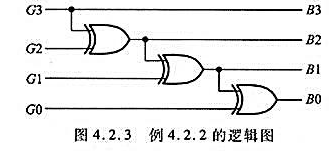

图4.2.3所示是一个码制变换器,将输入的格雷码转换成二进制码输出,试用Veril-ogHDL数据流方式描

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“图4.2.3所示是一个码制变换器,将输入的格雷码转换成二进制码输出,试用Veril-ogHDL数据流方式描”相关的问题

更多“图4.2.3所示是一个码制变换器,将输入的格雷码转换成二进制码输出,试用Veril-ogHDL数据流方式描”相关的问题

第1题

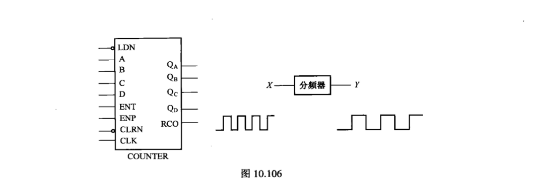

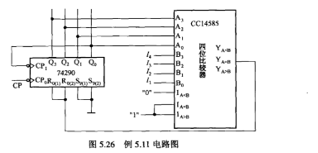

图5.26所示为一可变进制计数器,其模数受I4I3I2I1控制.其中,74290已通过将CP1与Q0短接而连成8421BCD码十进制加法计数器的形式,CP0为外部计数输入端, 为异步置0端,

为异步置0端, 为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端,

为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端, 为扩展输入端,

为扩展输入端, 为比较输出端.

为比较输出端.

(1)分析I4I3I2I1=0110时,该电路为多少进制计数器,并画出其状态转换图.

(2)简述该可变进制计数器的工作原理.

第2题

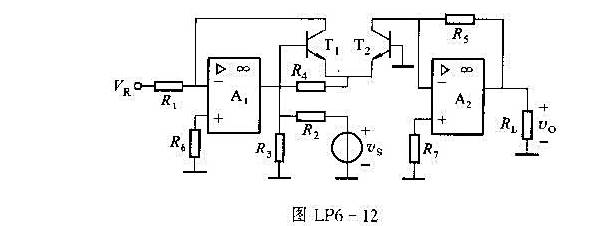

在图LP6-12所示的反对数变换器中,试证: ,其中τ=(R2+R3)/R3VT.已知VR=7V,R1=10kΩ,R2=15.7kΩ,R3=1kΩ,R5=10kΩ,试问:当υs由1mV变到10V时,在室温下相应υ0的变化范围是多少?

,其中τ=(R2+R3)/R3VT.已知VR=7V,R1=10kΩ,R2=15.7kΩ,R3=1kΩ,R5=10kΩ,试问:当υs由1mV变到10V时,在室温下相应υ0的变化范围是多少?

设各集成运放是理想的,各晶体管特性相同.

第3题

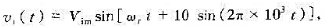

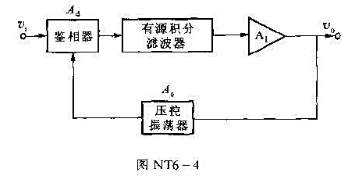

将图NT6-4所示的锁相环路用来解调调频信号。设环路的输入信号 ,已知,Ad=

,已知,Ad= ,有源比例积分滤波器的参数为

,有源比例积分滤波器的参数为 ,试求放大器输出1kHz的音频电压振幅VΩm。

,试求放大器输出1kHz的音频电压振幅VΩm。

第5题

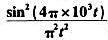

图10-26所示的连续时间信号抽样传输系统,已知系统的输入信号x(t)= ,抽样间隔T=0.1ms,图10-26中的信道滤波器是一个实的升余弦滚降带通滤波器,其频率响应

,抽样间隔T=0.1ms,图10-26中的信道滤波器是一个实的升余弦滚降带通滤波器,其频率响应 如图10-26(b)所示.试求:

如图10-26(b)所示.试求:

(1)x(t)的频谱X(w),并概画出X(w)以及xp(t)、y(t)的频谱Xp(w)、Y(w);

(2)试设计由系统输出y(t)恢复x(t)的系统,画出该恢复系统的方框图,并给出其中所用系统的系统特性(例如,滤波器的频率响应等).

第6题

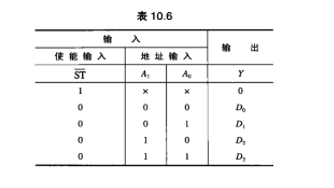

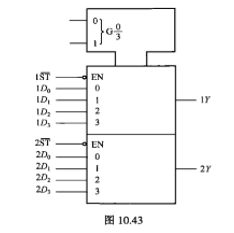

试用双4选1数据选择器74153和少量门设计一个有4个输入X3、X2、X1、X0和2个输出Y1、Y0的逻辑电路.电路输入为余3BCD码,输出为用2位二进制数表示的输入码中“1”的个数,例如,当输入X3X2X1X0=1010时,输出Y1Y0=10.当非余3码(伪码)输入时,要求输出Y1Y0=00.要求写出设计过程,画出电路图(规定X3、X2分别和数据选揮器地址码的高、低位相连接,74153的逻辑符号和功能表分别如图10.43和表10.6所示).

第7题

第8题

(1)画出系统的ASM图。

(2)画出系统的状态转换图。

(3)用Verilog HDL语言描述其工作过程。

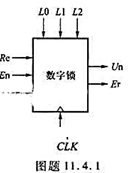

提示:数字锁系统的示意图如图题11.4.1所示,由于开锁过程比较简单,所以没有划分控制单元和处理单元。L0、L1、L2用于从到高位设置密码,另外三个输入端Re,En,Ki中,Re是复位端,当Re=

1时,系统复位进入初始状态;En是控制井关,Ki是数据输入端,当按一下En键使En=1时,从Ki端输入一个数码,再按一下En键,再送一个数码,直到将三个数码送完为止。每输入一个数据都要同原设定的密码比较,依次从低位到高位进行。若相等则准备接收下一位数码,若不相等,系统应进入错误状态。输入数码的位数也是开锁的条件。当输入数码的位数和位值与相应密码都相等时,系统发出开锁信号Un=1,锁被打开,否则Er=1表示开锁过程错误。为保密起见,中间错误状态不显示,并且不能返回初态,直到三个数码全部送完为止。

第9题